Sony vise l’imagerie à grande vitesse de grands capteurs

Sony a publié un article présentant son point de vue et son approche concernant l’évolution des capteurs d’images CMOS empilés. L’article démontre les ambitions de Sony de développer davantage des capteurs empilés qui seront capables d’imagerie à haute vitesse, en particulier en ce qui concerne les grands capteurs. Découvrez les options et technologies ci-dessous.

Vous trouverez ici ce nouvel article intitulé «Evolving Image Sensor Architecture through Stacking Devices» publié par Yusuke Oike, chercheur et développeur de l’architecture des capteurs d’images CMOS et de la technologie des appareils chez Sony Semiconductor Solutions. L’article démontre l’approche de Sony en matière de technologies empilées de capteurs d’images répondant à divers besoins. La taille de la puce des capteurs d’image varie en fonction de la taille optique, allant de 1/4 pouce (3,6 mm x 2,7 mm) utilisé dans les smartphones à 35 mm plein format (36 mm x 24 mm) utilisé dans les appareils photo grand public haut de gamme. De plus, entre les lignes, nous pouvons explorer le point de vue de Sony concernant l’imagerie à haute vitesse, qui est réalisée via différentes architectures. Nous avons conclu les points clés pertinents pour notre industrie (caméras grand public à grand capteur).

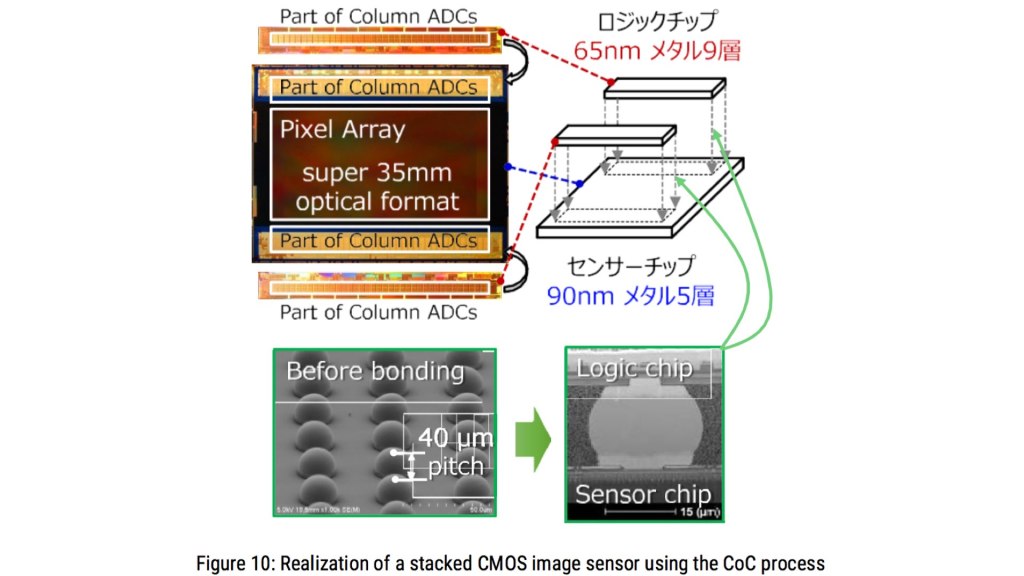

La diapositive ci-dessous montre une comparaison entre le processus Chip-on-Chip (CoC), qui empile les puces individuelles, et le processus Wafer-on-Wafer (WoW), qui empile les plaquettes ensemble. Les structures empilées grand public, principalement les capteurs d’images pour smartphones, utilisent le procédé WoW, qui présente l’avantage d’un rendement élevé, mais la taille de la puce du capteur et de la puce logique doit être la même. D’autre part, la structure empilée CoC permet aux puces logiques individuelles d’être attachées à la puce du capteur. En d’autres termes, la grande différence est qu’il n’est pas nécessaire d’attacher une grande puce logique à un capteur d’image avec une grande taille optique. Cependant, le processus CoC offre un avantage de coût par rapport au processus WoW lorsque la taille du circuit périphérique est suffisamment petite par rapport à la taille optique.

Un capteur d’image CMOS empilé utilisant le processus CoC est illustré dans le schéma ci-dessous. La taille optique est le format Super 35 mm (24 mm x 18 mm). À l’époque, la fonction d’obturateur global, qui permet une imagerie sans distorsion de sujets en mouvement, n’était disponible que dans les types à éclairage frontal. Le processus CoC est utilisé pour combiner la fonction d’obturateur global avec la fonction de prise de vue au ralenti à une résolution 4K dans une caméra de diffusion professionnelle haut de gamme, permettant l’enregistrement vidéo à 480 images par seconde à une résolution 4K de 8 mégapixels. Le processus CoC actuel n’est pas aussi productif que le processus WoW, mais comme les capteurs d’image deviennent plus sophistiqués et que des processeurs et des mémoires basés sur des processus CMOS avancés sont nécessaires, l’importance du processus CoC, qui a un degré élevé de liberté dans la sélection du processus pour chaque fonction, peut augmenter.

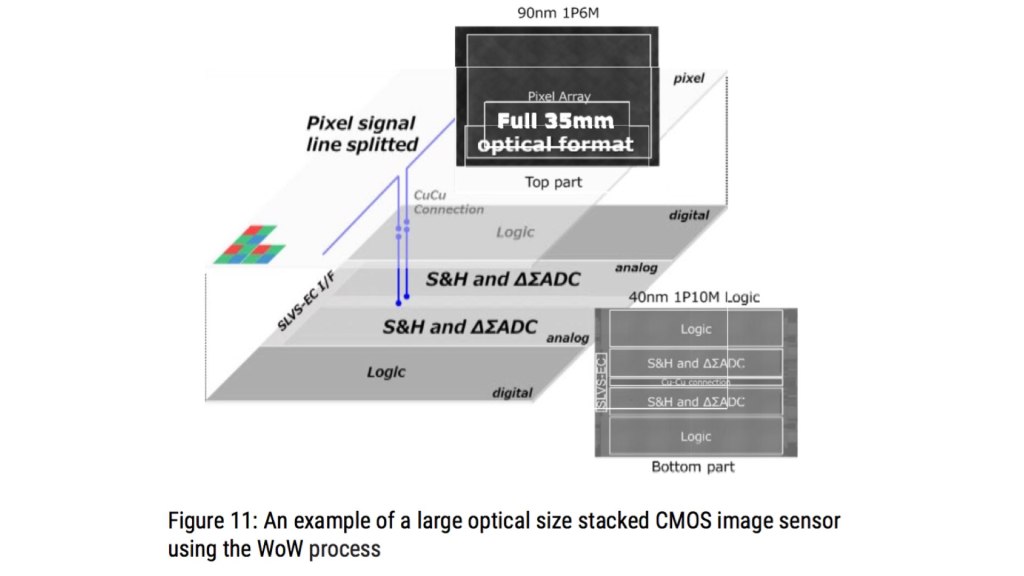

Le capteur dont il est question est un plein cadre, 50MP 250 FPS (très probablement le capteur de l’Alpha 1). La diapositive ci-dessous montre un exemple de capteur d’image CMOS empilé plein format 35 mm (36 mm x 24 mm) moderne utilisant le processus WoW. Comme mentionné précédemment, le processus WoW convient lorsque la taille du circuit périphérique correspond à la taille optique. Une fréquence d’images élevée de 250 images par seconde à 50 mégapixels est obtenue en utilisant plusieurs CAN ΔΣ parallèles qui peuvent fonctionner à grande vitesse avec un faible bruit pour les caméras à objectif unique haut de gamme.

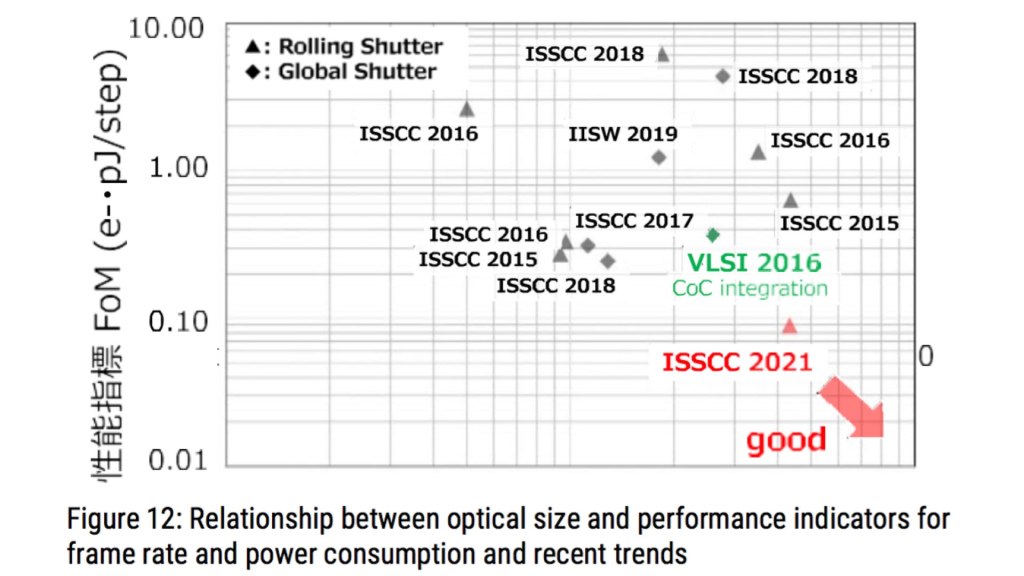

Une autre diapositive montre l’évolution du FoM (Figure of Merit), qui est un indice de performance du bruit équivalent électronique et de la consommation d’énergie par étape de conversion AD, par rapport à la taille optique. Même dans le cas des capteurs d’images grand format, où une vitesse élevée est difficile à atteindre, l’utilisation d’une structure empilée a conduit à des progrès continus dans l’obtention à la fois d’une vitesse élevée et d’une qualité d’image élevée.

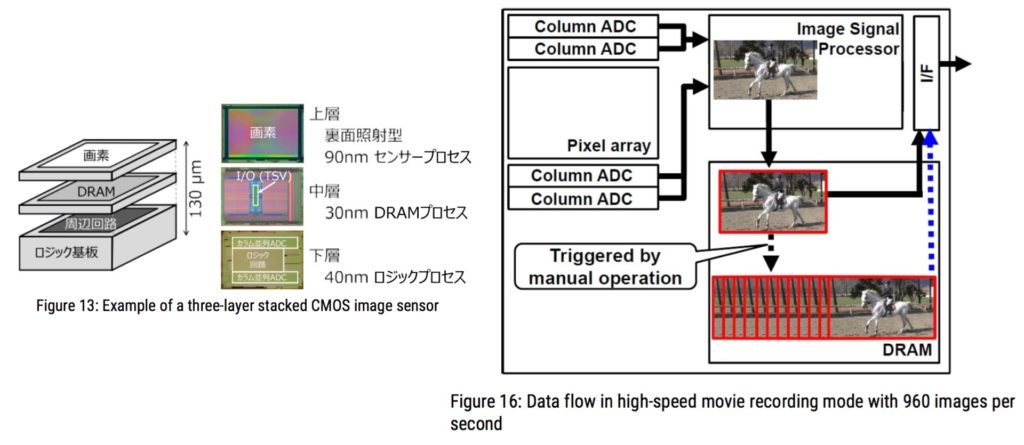

En empilant les DRAM directement sur le capteur d’image, un bus 200 MHz 512 bits peut être utilisé pour connecter les DRAM au processeur d’image. La DRAM est empilée directement sur le capteur d’image pour fournir une liaison de bande passante à faible consommation de 102 Gbit/s entre la DRAM et le processeur d’image. En utilisant la mémoire tampon DRAM, Sony a atteint un maximum de 960 images par seconde en résolution Full HD (1920 × 1080 pixels), comme illustré dans la diapositive 10. En mettant temporairement en mémoire tampon les données avant et après une scène au ralenti dans la DRAM, Sony capture jusqu’à à 960 images par seconde en résolution Full HD (1920 × 1080 pixels). Explorez la démonstration de schéma suivante de la DRAM dans une architecture empilée.

Sony utilise une architecture empilée afin d’élever le FPS (Frame Per Second) sur les grands capteurs (au-dessus du Super 35 mm), en se concentrant sur les caméras prosommateurs. Sony vise à améliorer à la fois les volets roulants et globaux sur CMOS, en particulier en ce qui concerne les capacités FPS. Comme indiqué, Sony a réussi à développer un capteur plein format 50MP capable de 250 PFS et un capteur empilé à obturateur global à grande vitesse. Cet article indique l’approche de Sony pour utiliser la DRAM dans une architecture empilée afin d’augmenter les FPS et ainsi d’atteindre des fréquences d’images ultra-élevées. Ces résultats suggèrent une nouvelle génération de capteurs d’image grand format capables de filmer des fréquences d’images ultra-élevées, combinées à un nombre de pixels très élevé, et sans altérer le facteur de forme compact des appareils photo.

Liste de produits

Voici les produits mentionnés dans l’article et les liens pour les acheter auprès des revendeurs agréés.

- Appareil photo numérique sans miroir Sony Alpha 1